内容大纲

如何在智慧教育中融入FPGA

数字系统设计实验操作

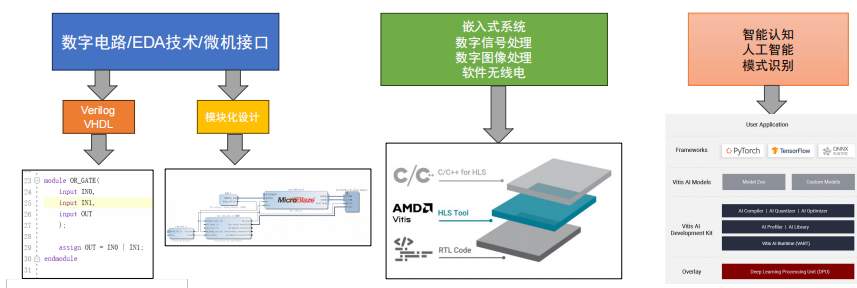

当下的FPGA开发方法

智慧教育大潮中FPGA与教育的结合

FPGA只是用作辅助专业知识学的一种工具

内容大纲

如何在智慧教育中融入FPGA

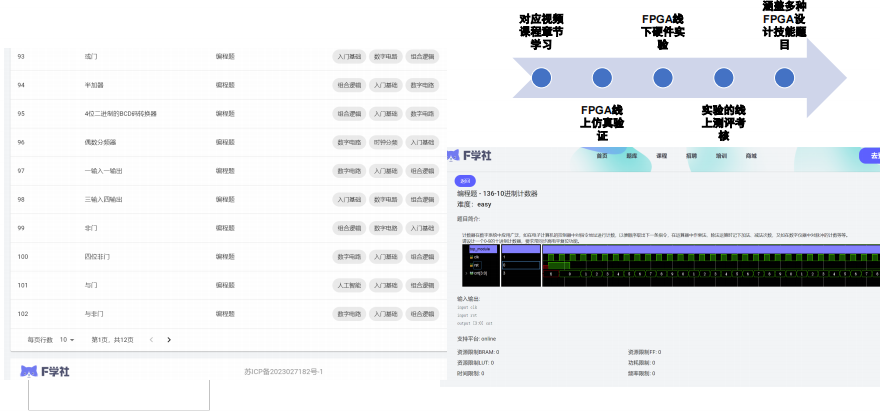

数字系统设计实验操作-部分案例

解决方法-构建智慧教育社区

解决方法-线上线下硬件平台

智慧+教育

智能化、互联化、开放化

硬件系统功能

• 通过无线传输的方式,实时将实验过程上传到智慧社 区。实时记录板卡上电,下载,FPGA芯片使用,板 卡接口,按键,LED,使用状态等实验信息。实时记录 传输采集到教师端直观展示。

解决方法-共享学科交叉融合的实验题库

解决方法-共建优质贯穿课程内容

解决方法-理论+实践课程考核认证

教师端功能

学生端功能

内容大纲

如何在智慧教育中融入FPGA

数字系统设计实验操作-部分案例

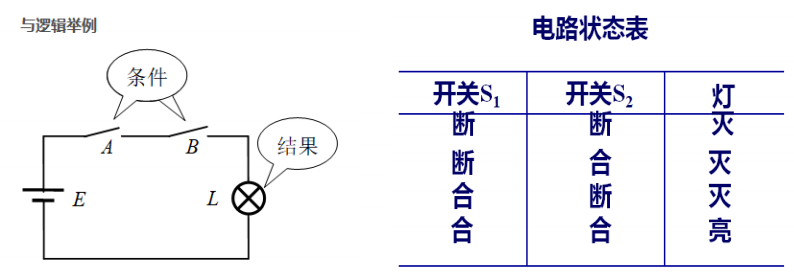

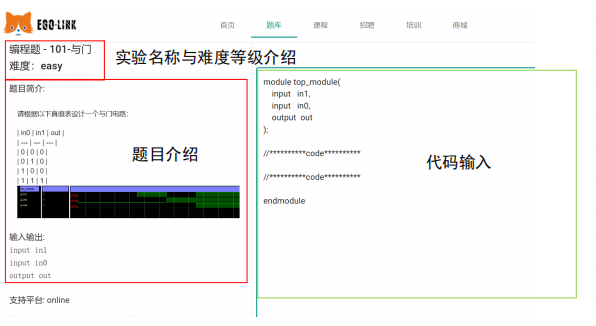

线上实验-与运算

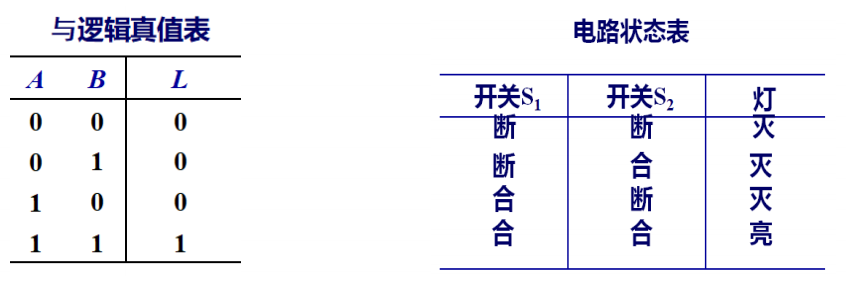

与逻辑:只有当决定某一事件的条件全部具备时,这一事件才会发生。这种因果关系称为与逻辑关系。

线上实验-与运算

与逻辑表达式

L=A&B

线上实验-与运算

线上实验- assign

verilog中的assign,可以看成是单向的物理连线,其作用是连续赋值。

线上实验-assign

代码示例(默认端口类型为wire):

module top (

input in,

output out );

assign out = in;

endmodule

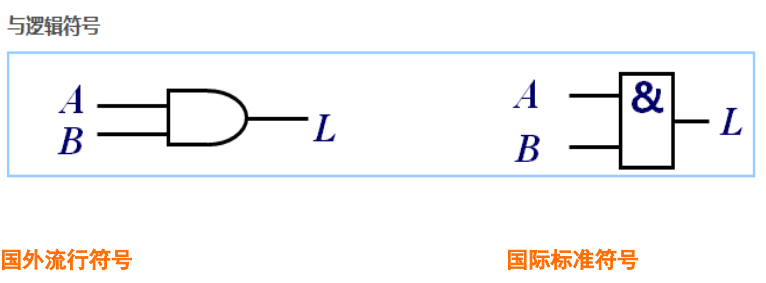

线上实验- assign连续赋值

连续赋值

线上实验- assign连续赋值

在Verilog中, wire 可以纯粹看作一根导线(或者任意位宽的总线)。在使用wire 时需要注意以下几点语法规则:

1,wire 类型用于将模块例化时的输入输出端口连接到你设计的电路的其他地方。

2,wire 类型在模块声明也作为输入输出。

3,wire 类型必须被其他东西驱动而不能用于存储数据。

4,wire 类型在 always@ 块中不能作为 = 或 <= 的左值。

5,wire 类型是 assign 语句中左值的唯一合法类型。

6,wire 类型可以将两个基于Verilog的设计相结合,是一种无状态的方法(并不是 很明白这里指的是什么意思)。

7,wire 类型只能用于组合逻辑建模。

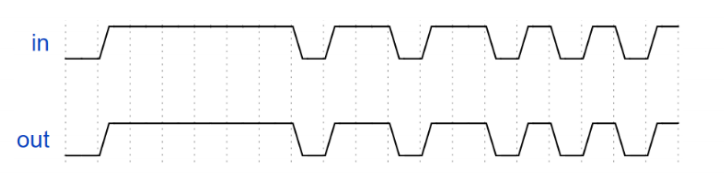

wire多位宽模块示意图

代码示例:

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 );

assign outv = vec;

assign o0 = vec[0];

assign o1 = vec[1];

assign o2 = vec[2];

endmodule

线上实验- 与运算

线上实验- 与运算

线上实验- 与运算

module top_module(

input in1,

input in0,

output out

);

//**********code**********

assign out = in1 & in0;

//**********code**********

endmodule

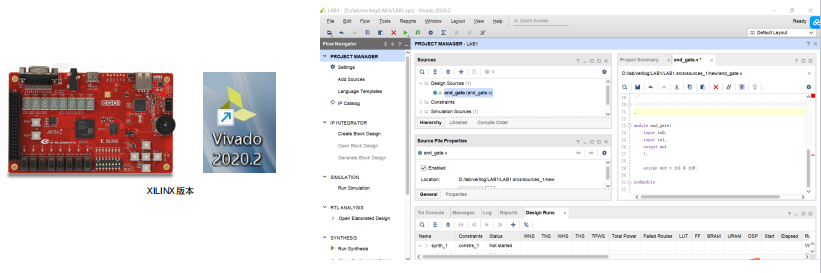

线下实验- 与运算 Verilog

硬件平台支持Xilinx / altera / 安陆 / 紫光 / 高云 /易灵思等

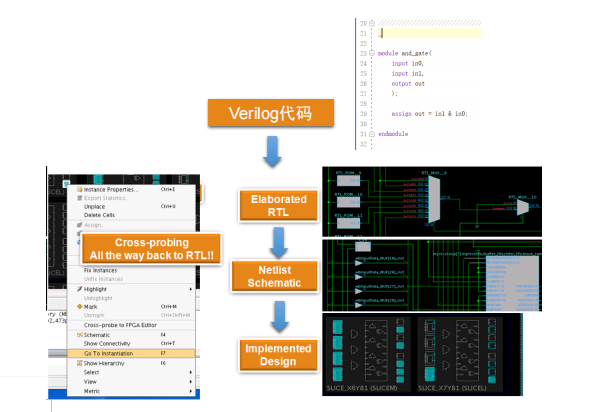

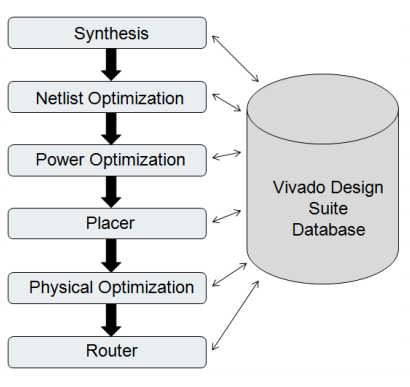

线下实验- VIVADO设计流程

线下实验- VIVADO设计流程